汇编语言第二章总结

2021-05-16 00:28

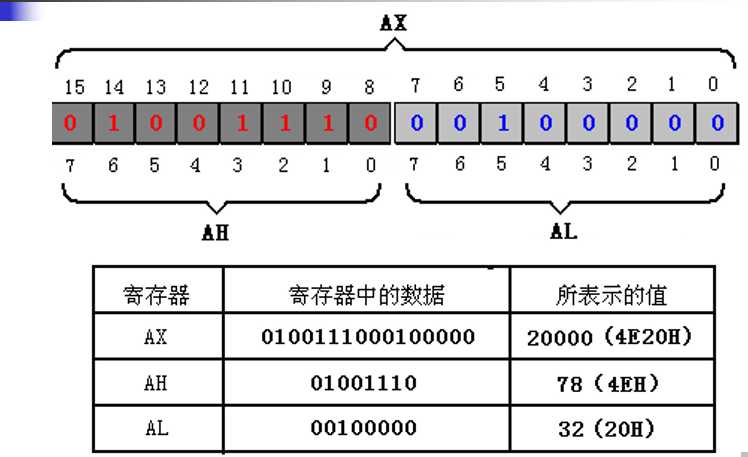

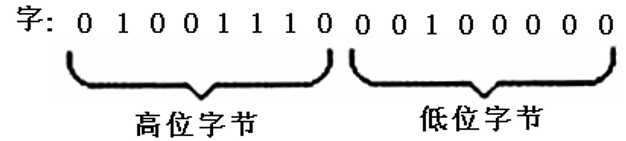

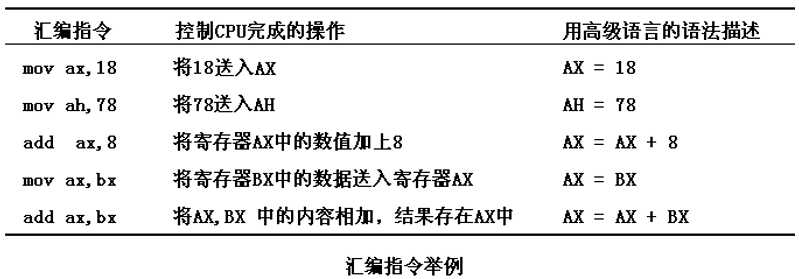

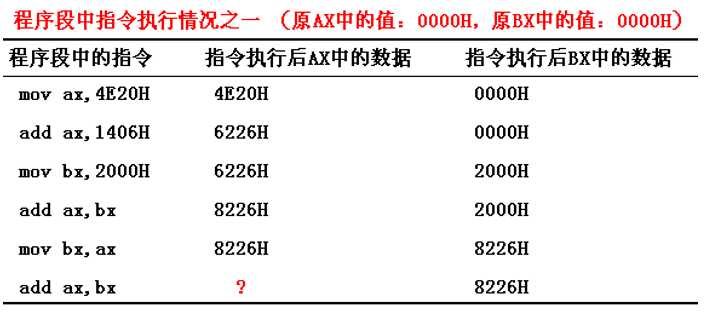

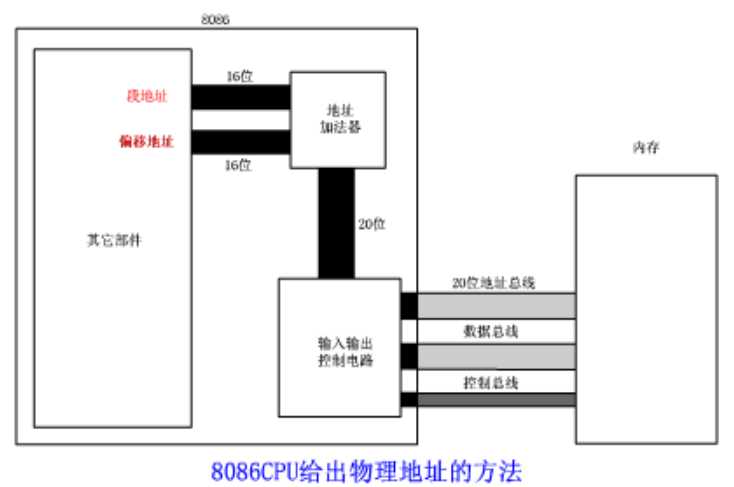

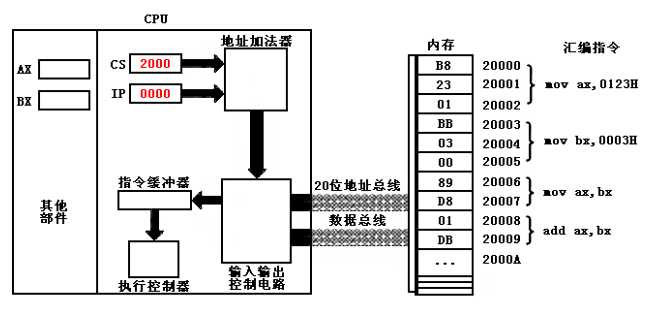

标签:常用 控制 red 寄存器 并且 bit 地址 本质 兼容 CPU的主要部件是寄存器,在8086CPU有14个寄存器,它们分别是:AX、BX、CX、DX、SI、DI、SP、BP、IP、CS、SS、DS、ES、PSW。8086CPU的所有寄存器都是16位的,可以存放两个字节。AX、BX、CX、DX这4个寄存器通常用来存放一般性的数据,称为通用寄存器。由于8086CPU的上一代CPU中的寄存器都是8位的,为了保持兼容,8086CPU的AX、BX、CX、DX这4个寄存器都可分为两个独立使用的8位寄存器: ?AX可分为AH和AL ?BX可分为BH和BL ?CX可分为CH和CL ?DX可分为DH和DL 出于兼容性的问题,8086CPU可以处理两种尺寸的数据: 字节:记为byte,一个字节由8个bit组成,可以存放在8位寄存器中 字:记为word,由两个字节组成,这两个字节分别被称为高位字节和低位字节 通过汇编指令控制CPU进行工作: 在写一条汇编指令或一个寄存器的名称时不区分大小写。 CPU执行程序段中的每条指令后,对寄存器中的数据的改变: 程序段中的最后一条指令add ax,bx,在执行前ax和bx中的数据为8226H,相加后的数据为:1044CH,但是ax为16位的寄存器,只能存放4位十六进制的数据,所以最高位的1不能在ax中保存,ax中的数据为:044CH,最高位的1并不是舍去了,而是存在了其他位置,随着我们对汇编语言的慢慢深入,就会体会到程序设计师的聪明与机智。 注意:ax分出的两个独立的寄存器ah与al,它们是毫无关联的,不要误认为al的数据相加后超出的位数存放在ah中! 每一个内存单元都有唯一的地址,称为物理地址。 16位结构的8086CPU: 1.运算器一次最多可以处理16位的数据。 2.寄存器的最大宽度为16位。 3.寄存器和运算器之间的通路为16位。 8086CPU有20位地址总线,可以达到1MB的寻址能力,那它怎么用16位地址来达成20位物理地址的呢? 8086CPU采用在内部用两个16位地址合成的方法来形容一个20位的物理地址。 逻辑结构如图所示: 地址加法器采用:物理地址=段地址*16+偏移地址的方法进行合成 “物理地址=段地址*16+偏移地址”本质含义:CPU在访问内存时,用一个基础地址(段地址*16)和一个相对于基础地址的偏移地址相加,给出内存单元的物理地址。 段的概念:每一个段有一个段地址,但是内存并不是被划分成一段一段的,而是由于CPU进行划分。 由于16位地址的寻址能力是64KB,所以一个段的最大长度为64KB,并且段的起始地址一定是16的倍数,变化范围为0~ffffH。 8086CPU有4个段寄存器:CS,DS,SS,ES。 CS和IP是8086CPU中两个最关键的寄存器,CS为代码段寄存器,IP为指令指针寄存器。 8086CPU读取、执行的工作原理: CS和IP的值是可以修改的:IP每次是根据指令的空间大小进行更新。 简单的修改CS、IP的指令:jmp指令。 ①同时修改CS、IP的内容:jmp段地址:偏移地址 ②只修改IP的内容:jmp 某一合法寄存器 汇编语言第二章总结 标签:常用 控制 red 寄存器 并且 bit 地址 本质 兼容 原文地址:https://www.cnblogs.com/1359027962qqcom/p/9750372.html