win8中如何通过新打开的窗口进行打开或保存文件

2020-12-02 08:32

标签:lcd 驱动 linux 嵌入式 arm9 一.硬件基础

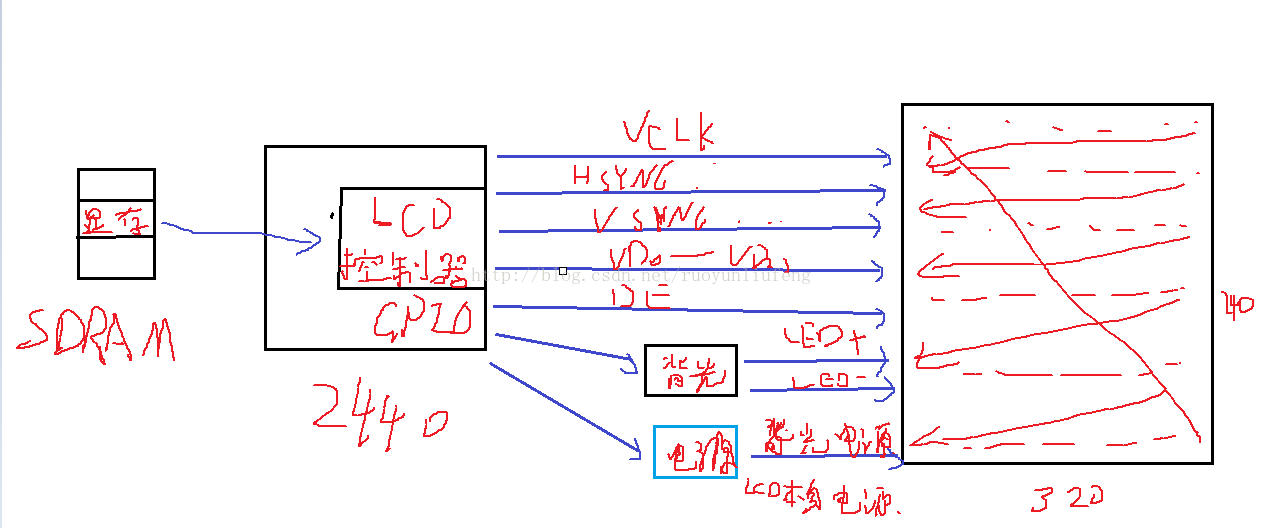

1.硬件框图

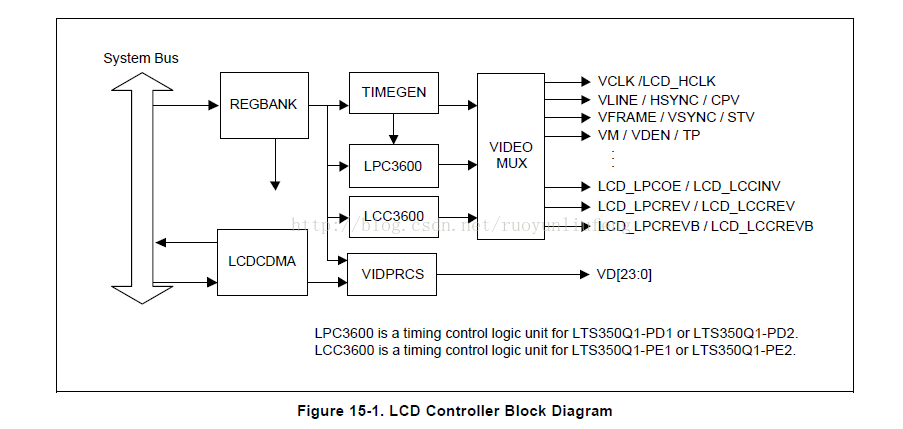

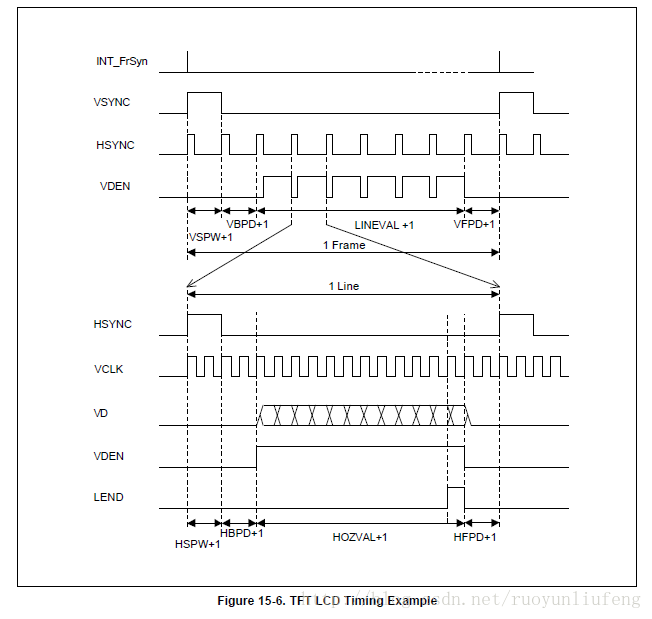

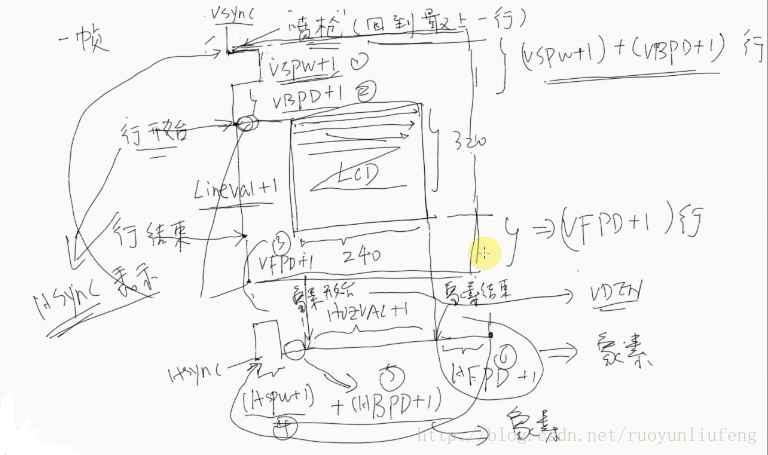

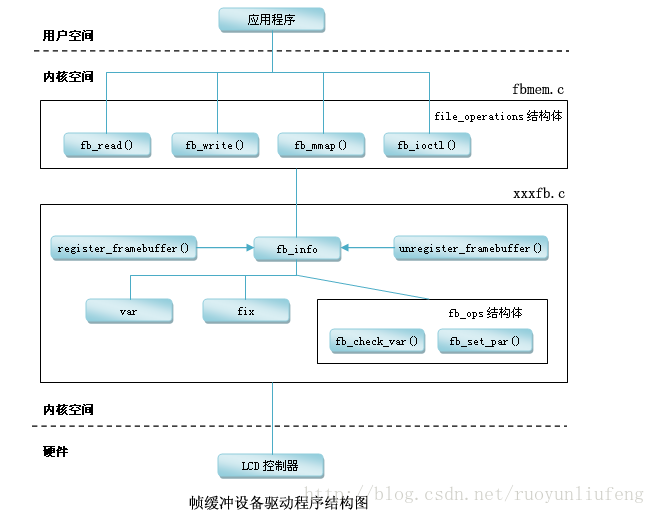

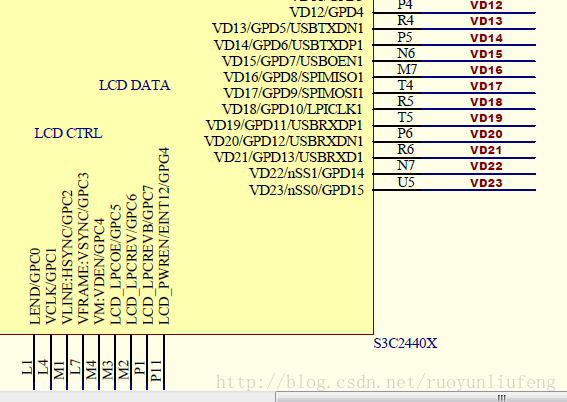

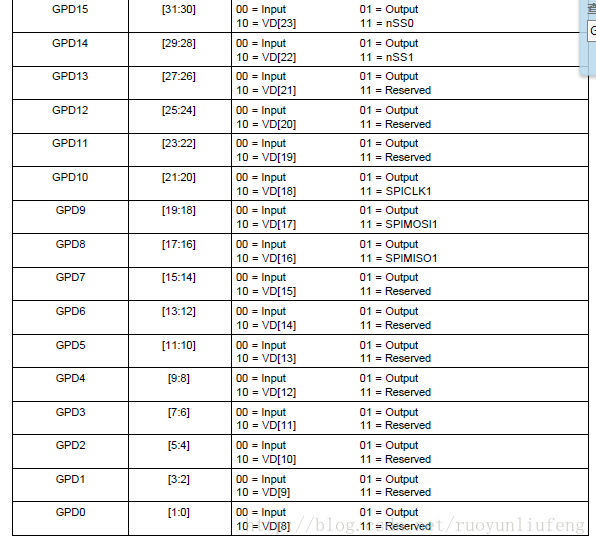

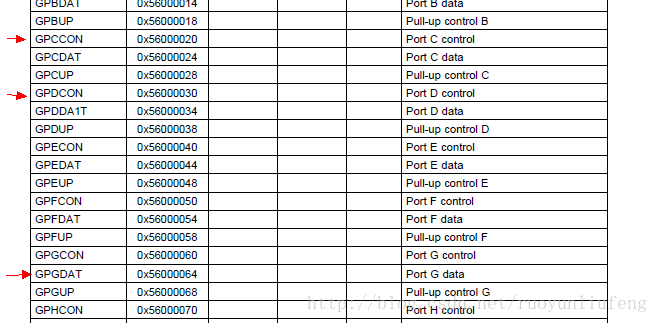

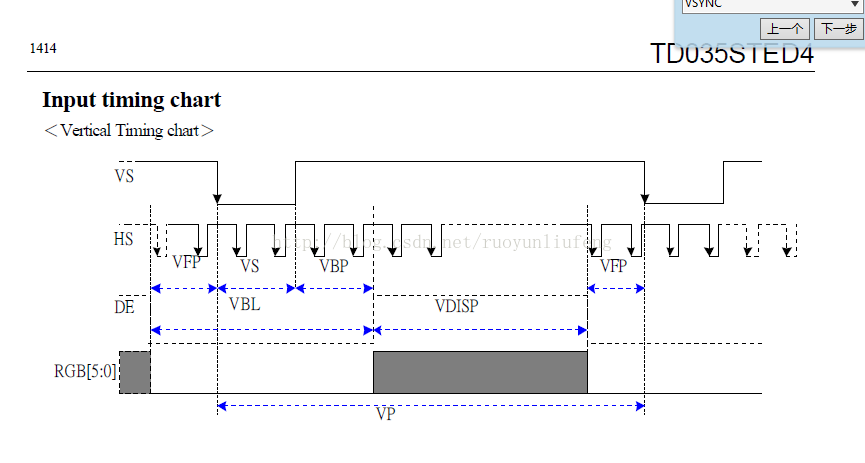

2.LCD控制器 了解硬件最直接的办法就是看手册,在这里我只会简单介绍下LCD的硬件。具体的我会在下面结合程序讲解。 a.REGBANK是LCD控制器的寄存器,含17个寄存器以及一块256*16的调色内存,用来设置各项参数。 b.LCDCDMA是LCD控制器专用的DMA信道。 c.TIMEGEN和LPC3600负责产生LCD屏所需要的控制时序。 d.VIDPRCS需要与LCDCDMA中的数组合成特定的格式,然后从VD[23:0]发送给LCD屏幕。 3.时序理解 二.驱动框架 三.改写驱动

1.程序代码

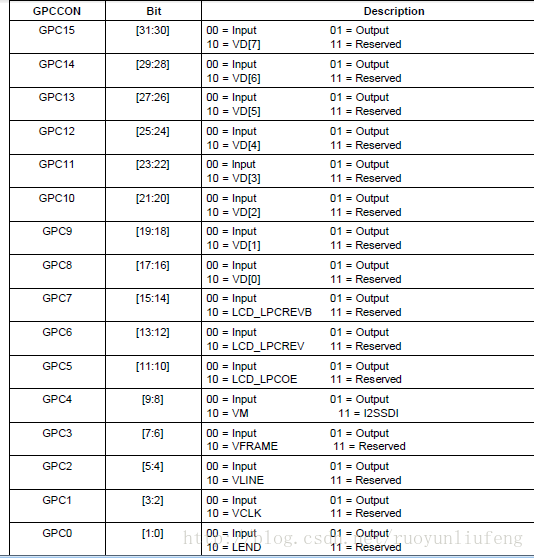

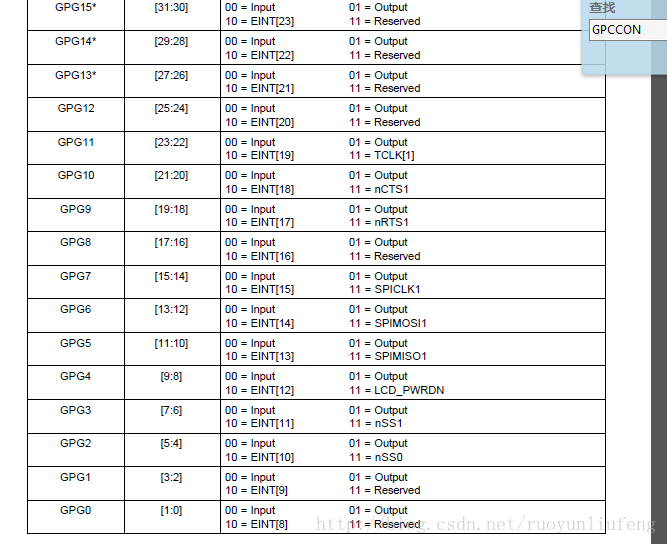

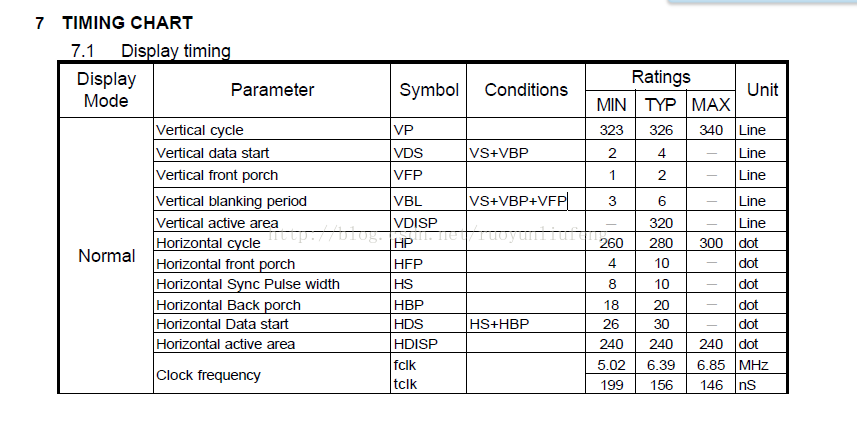

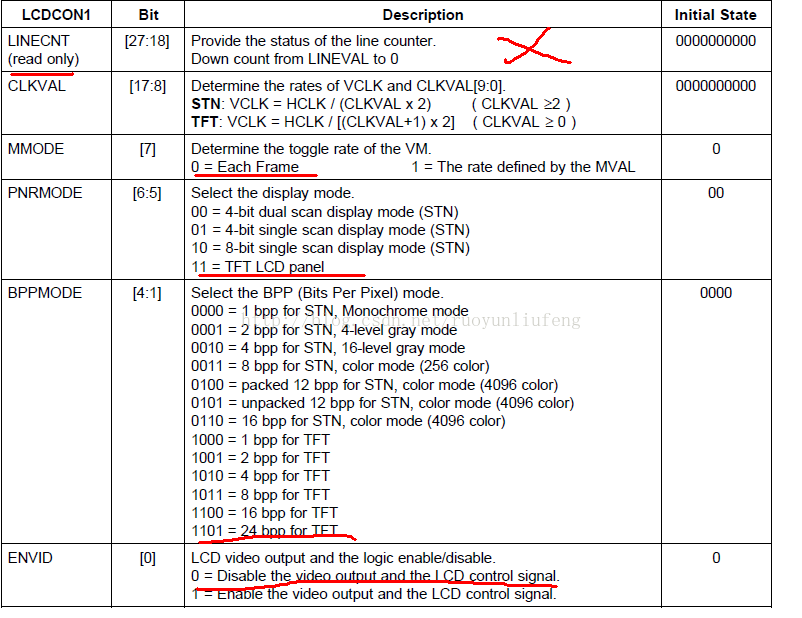

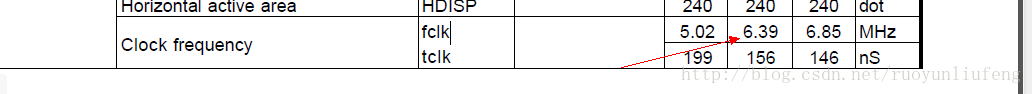

2.功能实现 (LCD四部曲) a. 分配一个fb_info结构体: framebuffer_alloc 上面框图我们可以知道,我们所有的操作都是通过fb_info结构体与上面交互的。所以首先先分配一个结构体。 b. 设置 1.设置固定参数 参考\linux-2.6.22.6\linux-2.6.22.6\include\linux\fb.h中的struct fb_fix_screeninfo { } 2.设置可变参数 参考\linux-2.6.22.6\linux-2.6.22.6\include\linux\fb.h中的struct fb_var_screeninfo{ } 3.设置操作函数 4.其他设置 c.硬件相关的操作 1.配置GPIO用于LCD 相信看了上面的手册,应该明白为什么这么设置了。0xaaaaaaaa就是都设成了1010......(相信小伙伴都懂我说的是啥了) 2.根据LCD手册设置LCD控制器, 比如VCLK的频率等 这个是重点,一般改写LCD只改写这里就行了。 首先建立映射,LCD Controller比较多,我们把它放到一个结构体里面。 下面开始设置比较重要的几个寄存器: 首先贴出LCD手册中的设置 a. LCDCON1 LINECNT只读的不用设置 CLKVAL根据公式TFT: VCLK = HCLK / [(CLKVAL+1) x 2] 根据 6.39MHz = 100MHz

/ [(CLKVAL+1) x 2]可以算出CLKVAL约等于CLKVAL

= 7

VCLK是根据LCD芯片手册上 MMODE为0

PNRMODE为11 TFT模式 BPPMODE 为1101 = 24 bpp for TFT ENVID

先设置为0

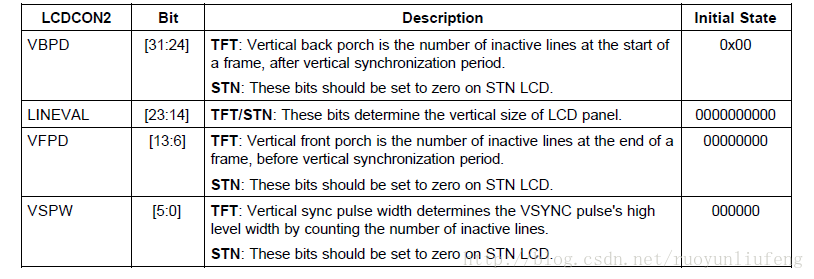

b. LCDCON2

/* 垂直方向的时间参数

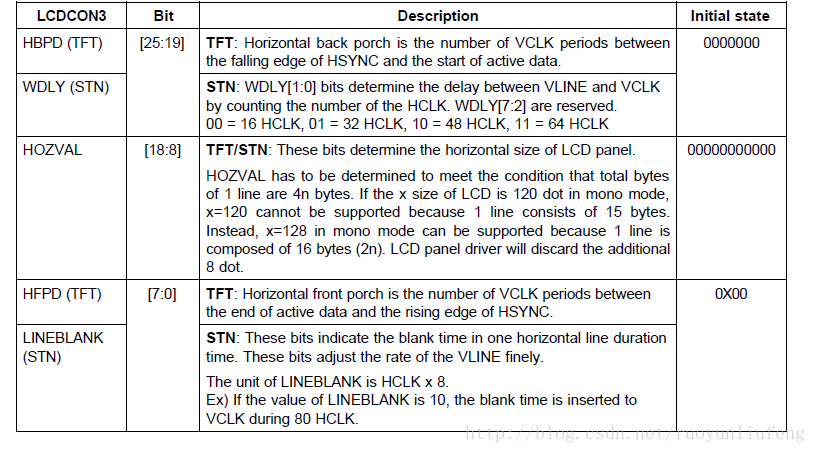

c. LCDCON3

/* 水平方向的时间参数

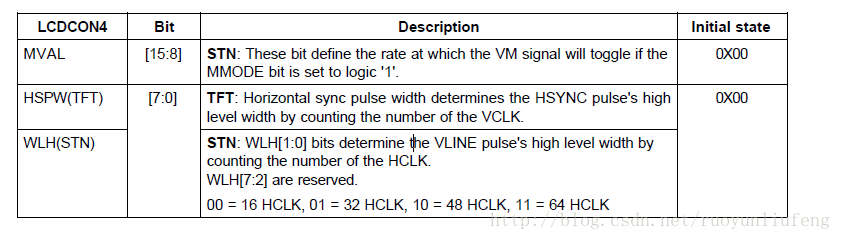

d. LCDCON4

/* 水平方向的同步信号

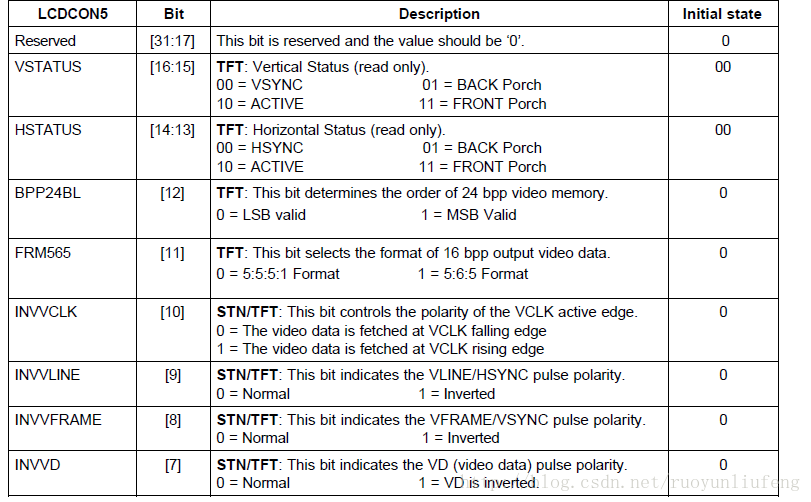

e. LCDCON5 /* 信号的极性 3.分配显存(framebuffer), 并把地址告诉LCD控制器 a.分配

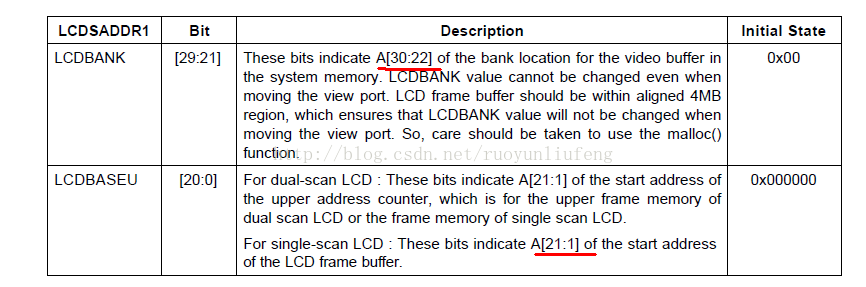

b.设置 LCDSADDR1 我们只需要将LCD地址右移1位置。然后将前两位(没用到的)清零即可。

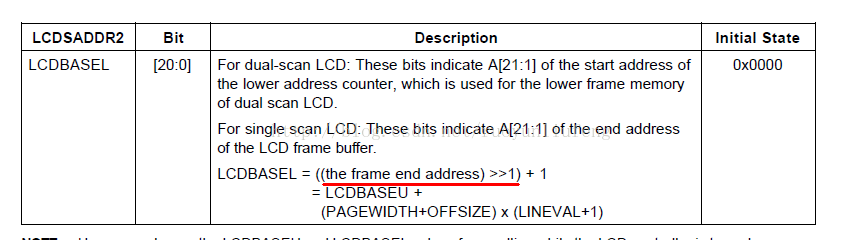

这里用到结束地址(其实就是开始地址+长度)然后右移动1位,最后将没用到的位清零。

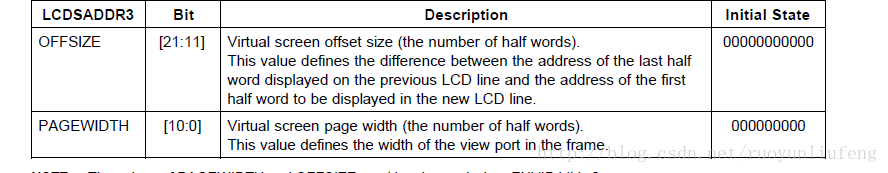

LCDSADDR3 表示的一行的长度,用半字(2字节)表示:

我们做的这些要叫内核知道,所以最后要注册一下 参考:韦东山视频二期 黄刚的S3C2440上LCD驱动(FrameBuffer)实例开发讲解

www.linuxidc.com/Linux/2011-03/33600.htm win8中如何通过新打开的窗口进行打开或保存文件 标签:lcd 驱动 linux 嵌入式 arm9 原文地址:http://blog.csdn.net/u010792238/article/details/24706097

#include

* 根据数据手册

* bit[31:24]: VBPD, VSYNC之后再过多长时间才能发出第1行数据

* LCD手册 2

* VBPD=17

* bit[23:14]: 多少行, 320, 所以LINEVAL=320-1=319

* bit[13:6] : VFPD, 发出最后一行数据之后,再过多长时间才发出VSYNC

* LCD手册2

* bit[5:0] : VSPW, VSYNC信号的脉冲宽度, LCD手册tvp=1, 所以VSPW=1-1=0

*/

* bit[25:19]: HBPD, VSYNC之后再过多长时间才能发出第1行数据

* LCD手册 20

* bit[18:8]: 多少列, 240, 所以HOZVAL=240-1=239

* bit[7:0] : HFPD, 发出最后一行里最后一个象素数据之后,再过多长时间才发出HSYNC

* LCD手册10

*/

* bit[7:0] : HSPW, HSYNC信号的脉冲宽度, LCD手册HSPW=10

*/

* bit[11]: 1=565 format, 对于24bpp这个不用设

* bit[10]: 0 = The video data is fetched at VCLK falling edge

* bit[9] : 1 = HSYNC信号要反转,即低电平有效

* bit[8] : 1 = VSYNC信号要反转,即低电平有效

* bit[6] : 0 = VDEN不用反转

* bit[3] : 0 = PWREN输出0

*

* BSWP = 0, HWSWP = 0, BPP24BL = 0 : 当bpp=24时,2440会给每一个象素分配32位即4字节,哪一个字节是不使用的? 看2440手册P412

* bit[12]: 0, LSB valid, 即最高字节不使用

* bit[1] : 0 = BSWP

* bit[0] : 0 = HWSWP

*/ s3c_lcd->screen_base = dma_alloc_writecombine(NULL, s3c_lcd->fix.smem_len, &s3c_lcd->fix.smem_start, GFP_KERNEL);

lcd_regs->lcdsaddr1 = (s3c_lcd->fix.smem_start >> 1) & ~(3 LCDSADDR2

lcd_regs->lcdsaddr2 = ((s3c_lcd->fix.smem_start + s3c_lcd->fix.smem_len) >> 1) & 0x1fffff;

lcd_regs->lcdsaddr3 = (240*32/16); /* 一行的长度(单位: 2字节) */

d.注册: register_framebuffer